Overview

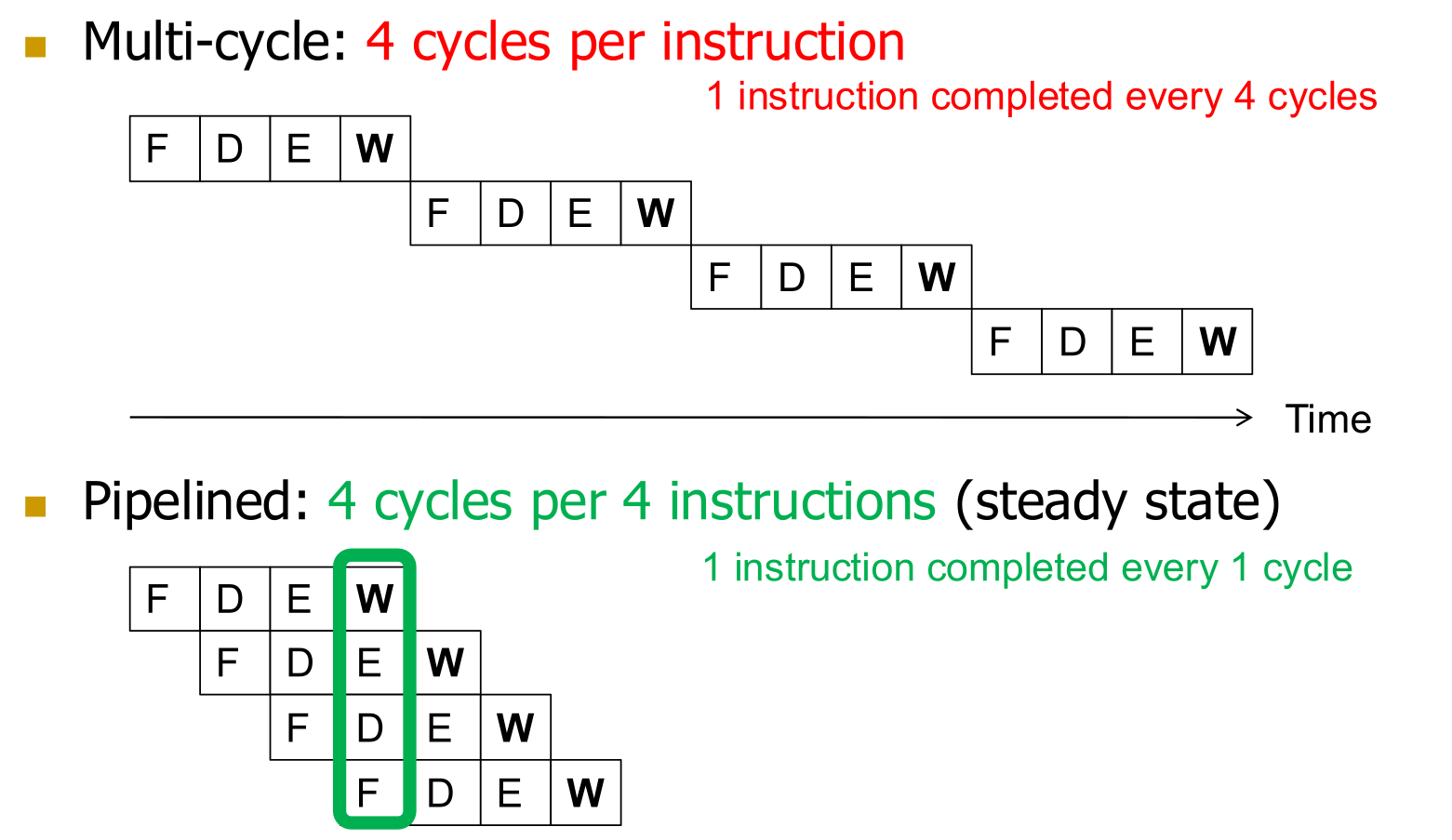

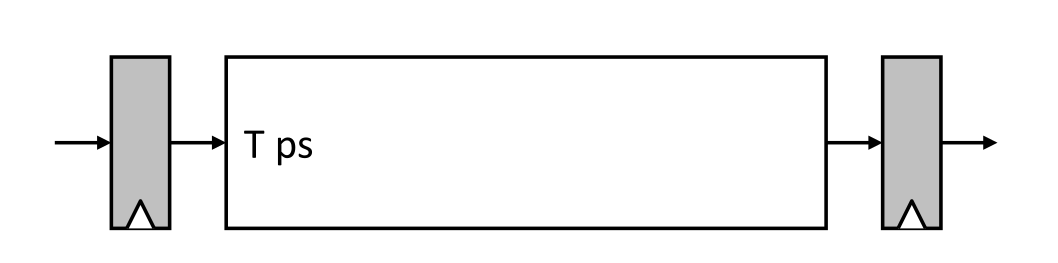

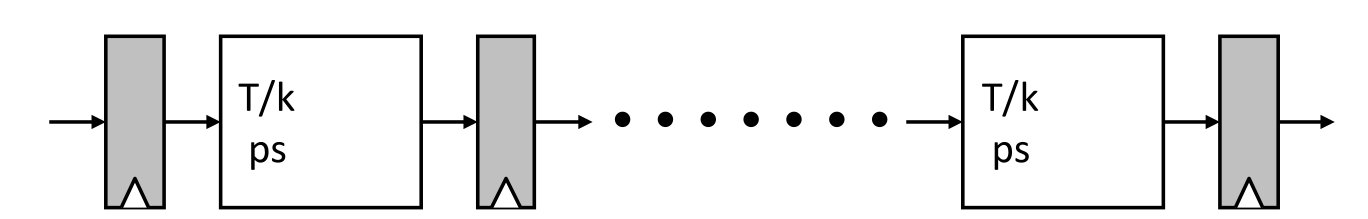

We divide the instruction into different stages

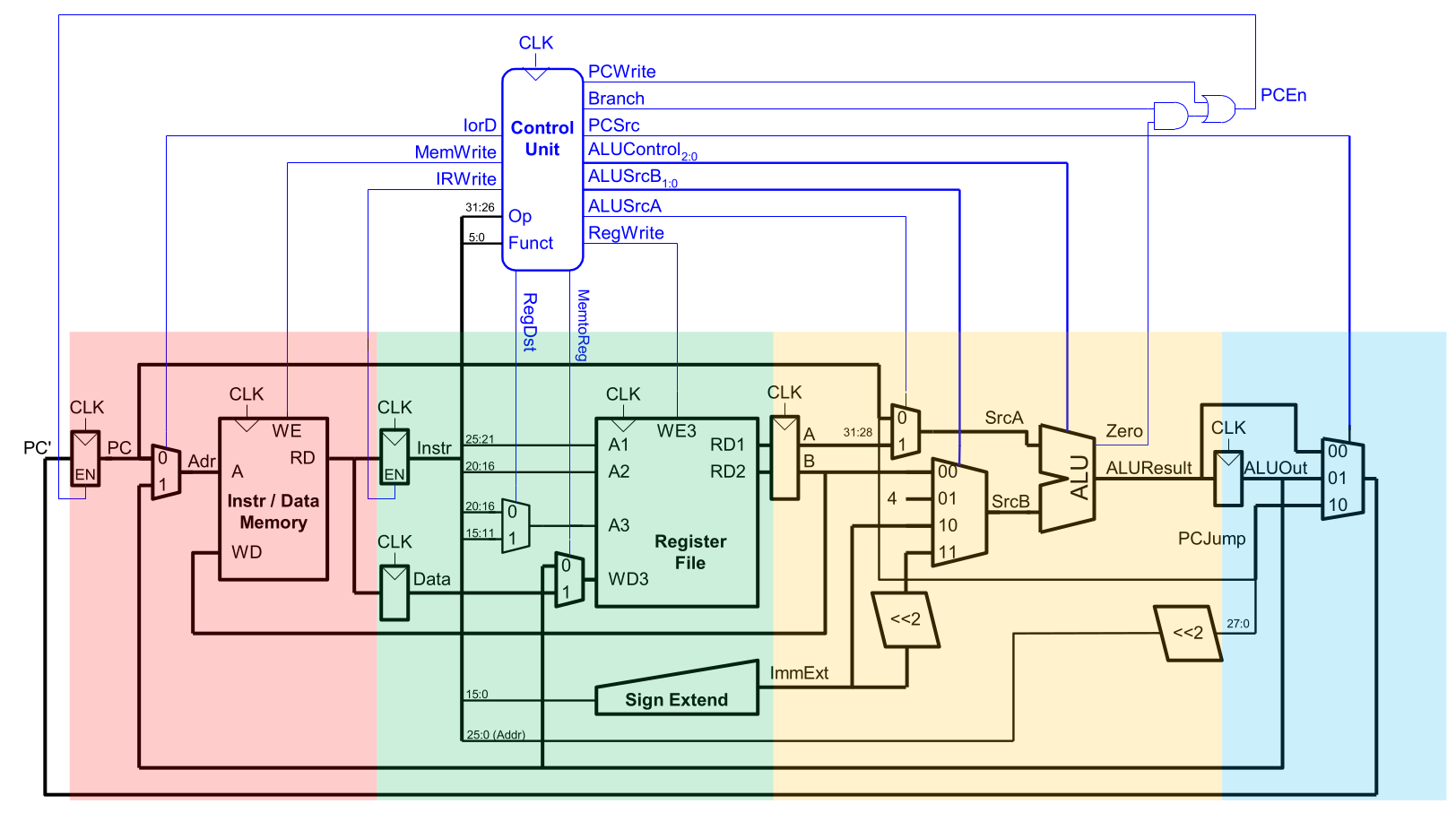

(for explanation of the design see Multicycle Processor)

(for explanation of the design see Multicycle Processor)

The basic idea to fully utilize the idle stages

An ideal pipeline

Goal: increase throughput with little increase in hardware cost.

An ideal pipeline works best when:

- the same operation is repeated on many different inputs

- the repeated operations are independent

- there are no dependencies between successive operations

- processing can be divided into uniform-latency suboperations

- the suboperations do not share resources

Example: many laundry loads go through the same sequence of steps.

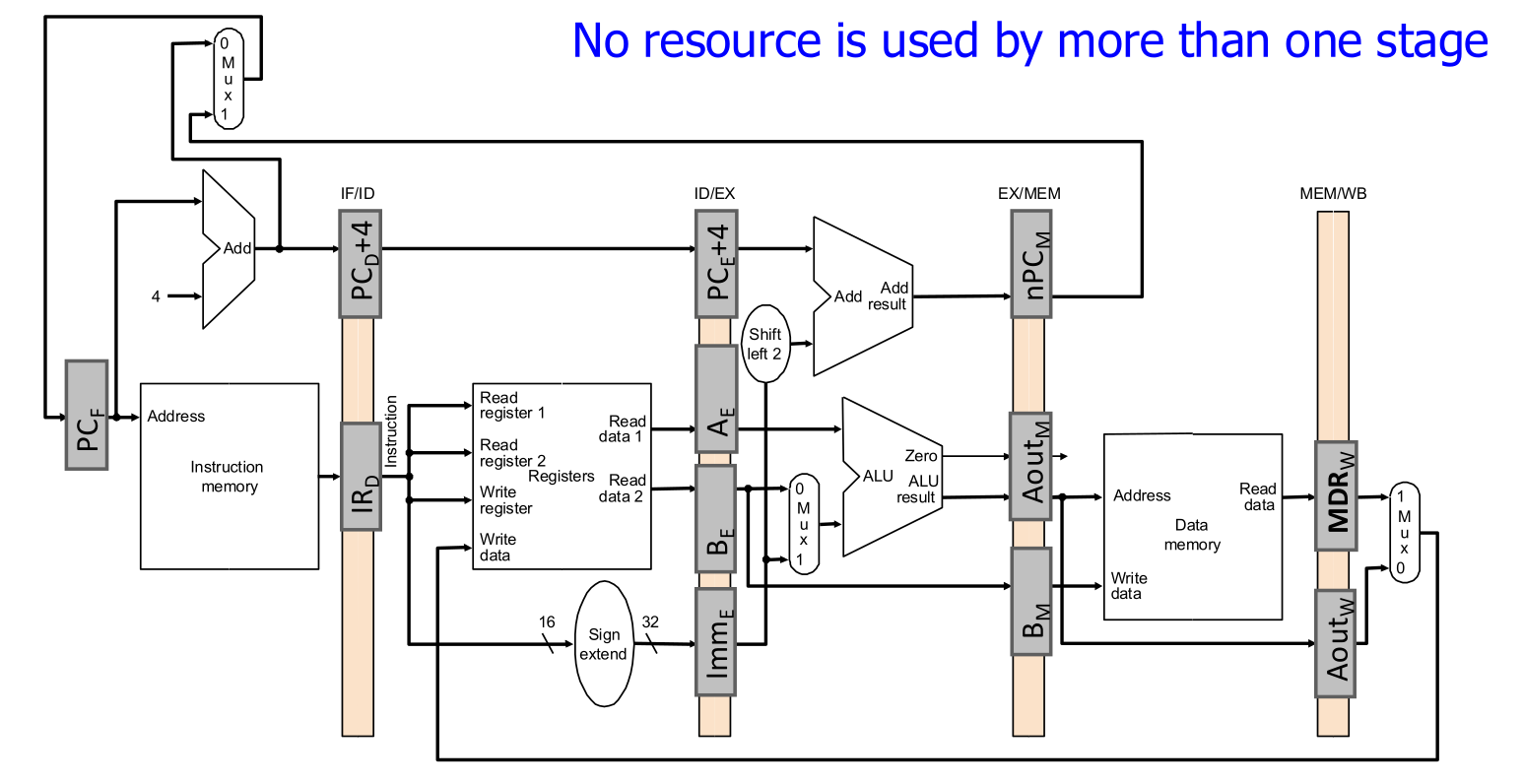

Full Design:

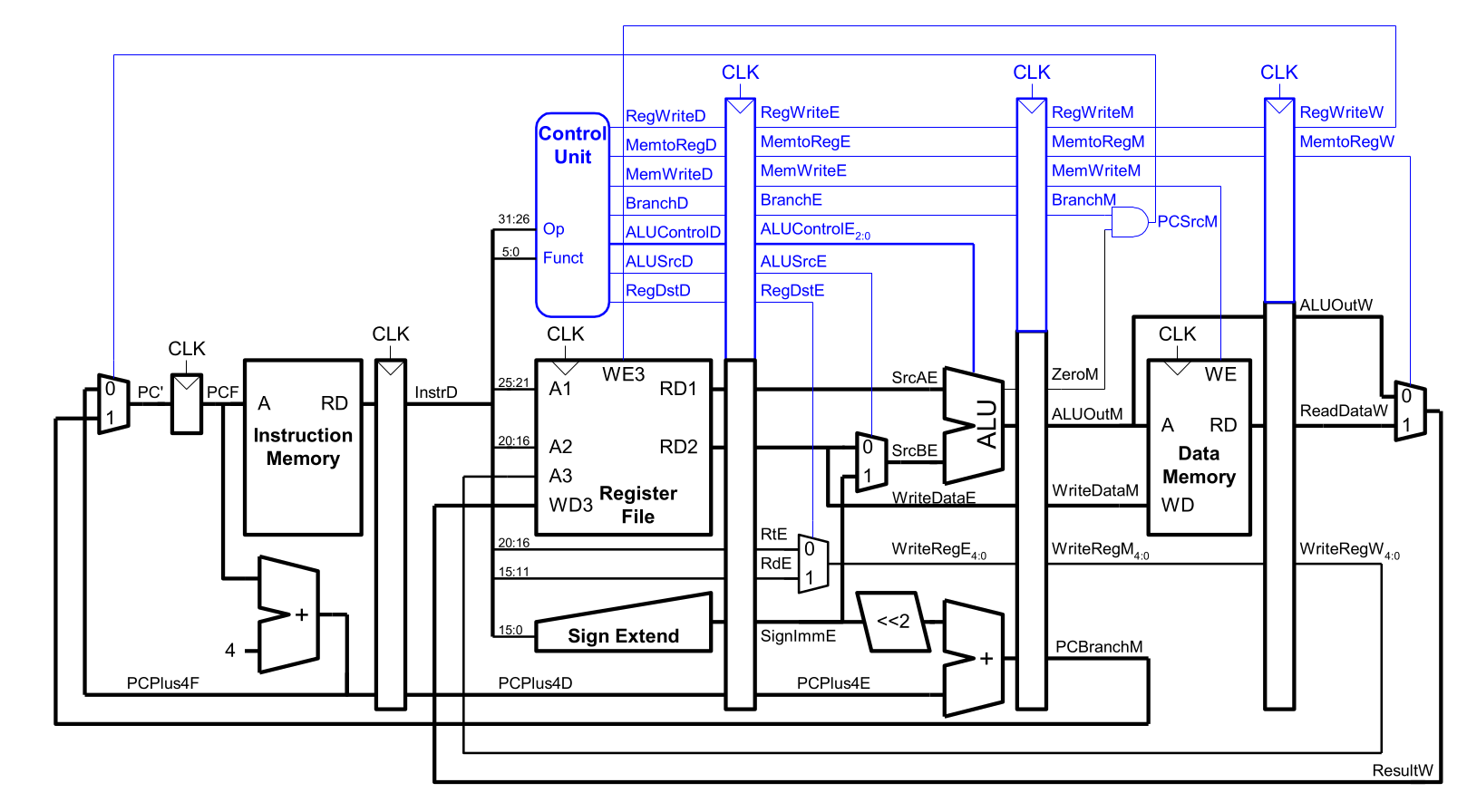

Full Design:

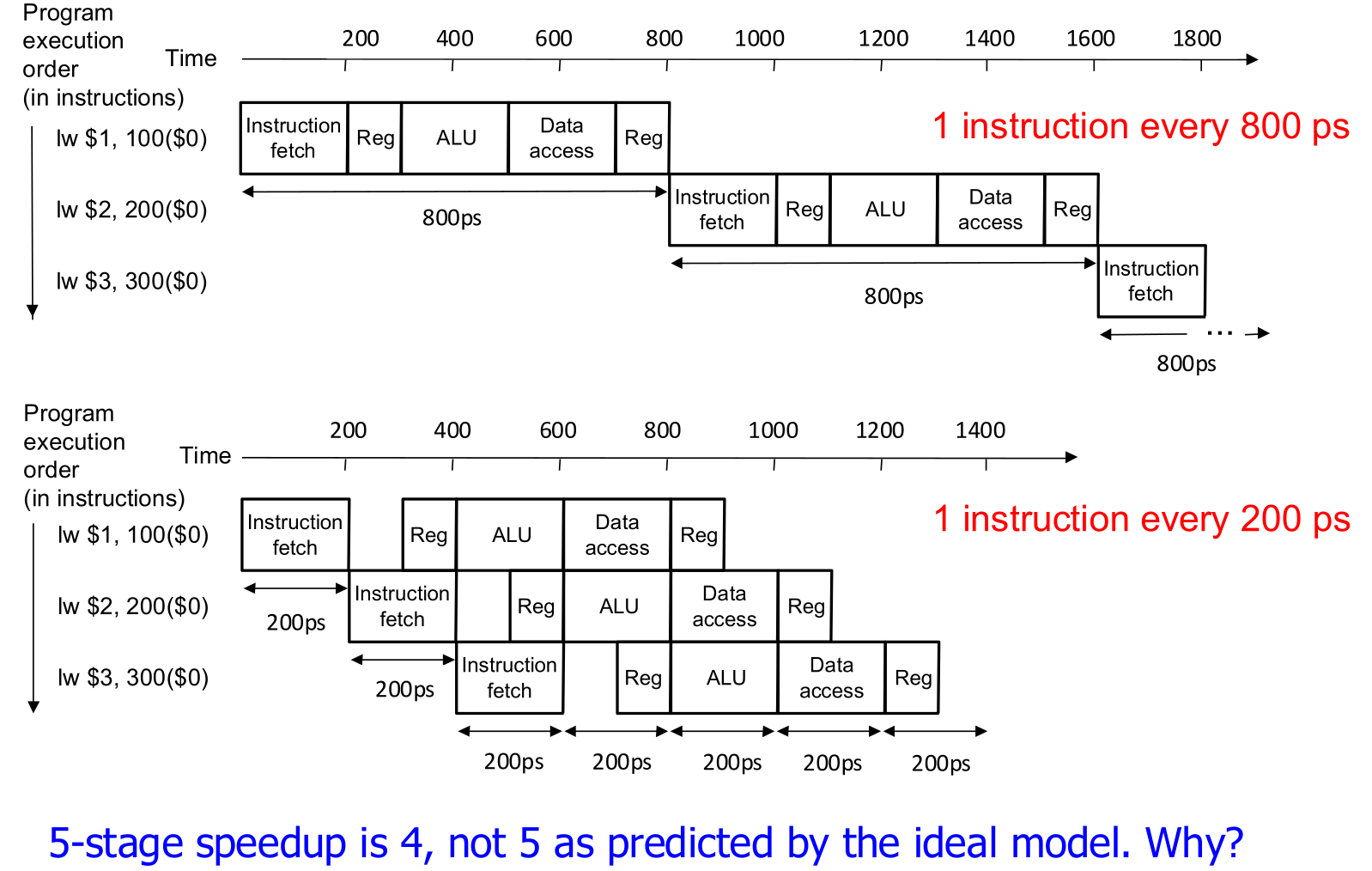

realistic throughput

Let

- : total combinational delay

- : register delay

Then for a nonpipelined design,

For an ideal -stage pipeline with perfectly balanced stages,

So pipelining increases throughput, but the register delay limits the gain. Even with many stages, the throughput cannot improve beyond the overhead caused by the pipeline registers.

NOTE

This assumes perfect division of work between stages.

However, stage division are usually not perfect:

Cost of pipelining

Let

- : combinational logic cost

- : register cost

Then for a nonpipelined design,

For a -stage pipeline,

So pipelining improves throughput, but it also increases hardware cost because more registers are needed.